Ein Forschungsschwerpunkt liegt bei sogenannten Depleted Monolithic Active Pixel Sensors (DMAPS) Detektoren, bei denen der eigentliche Sensor und die bisher separate Front-end-Elektronik auf CMOS-Basis in einem physischen Silizium-Block vereint sind. Da für die Ladungssammlung üblicherweise hohe elektrische Spannungen notwendig sind, werden diese Detektortypen auch HV-CMOS genannt. Diese Technologie erlaubt einen sehr platzsparende und ultra-leichten Aufbau eines Vertex- und Spurdetektors in HEP-Experimenten und ermöglicht daher hochpräzise Messungen, die kaum an unerwünschter Vielfachstreuung im Detektor leiden.

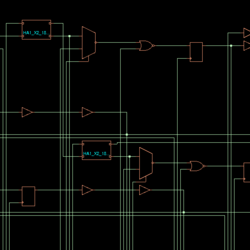

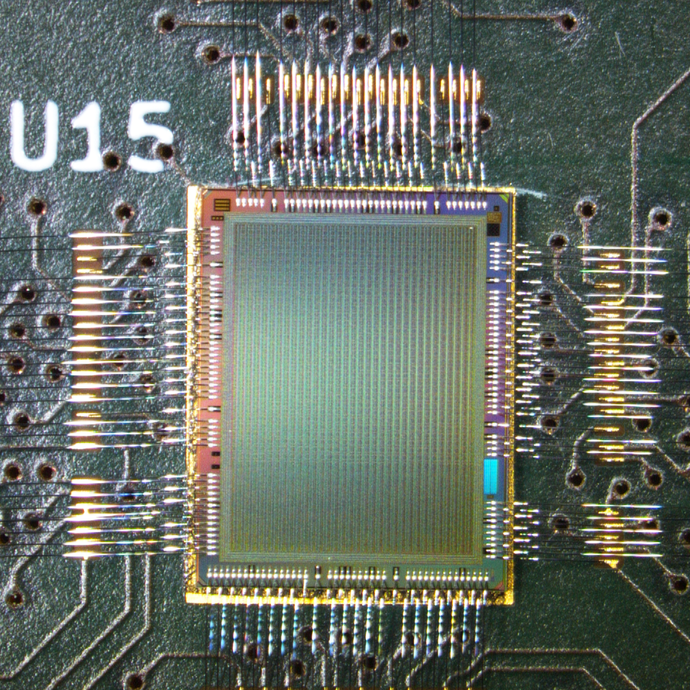

Die Produktion dieser Detektoren findet in kommerziellen Chip-Fabriken, sogenannten Foundries, statt und ist ein teurer und langwieriger Prozess. Aus diesem Grund beschäftigen wir uns ausgiebig mit dem Design und der Simulation dieser Sensoren, wo die gleichen Tools wie in der Chipindustrie (Cadence, Cliosoft, Mentor,..) verwendet werden. Da hier sowohl analoge Elektronik (Ladungssammlung im Detektorteil), als auch Digitalelektronik (ADC, Signalverarbeitung, Speicherung) auf kleinstem Raum zusammenarbeiten müssen, ist diese Aufgabe eine große Herausforderung und benötigt Detektorkenntnis, Elektronikwissen und Softwareexpertise gleichermaßen.

Des weiteren forschen wir auch an einem offenen Chipdesign auf Basis von Open-Source Software (magic, KLayout,..) und nutzen dies mit offenen PDKs wie Skywater 130nm über die efabless Initiative.

Entwicklungen im Rahmen von RD50

RD50 ist eine Forschungs- und Entwicklungszusammenarbeit des CERN, deren Hauptaugenmerk auf der Entwicklung von strahlungsharten Halbleiterbauelementen für Beschleuniger mit hoher Luminosität liegt. In den letzten Jahren wurden diese Bemühungen auch auf die Entwicklung monolithischer aktive Pixelsensoren auf Substraten mit hohem spezifischem Widerstand ausgedehnt, wo 17 Institute an ASIC Design, TCAD Simulationen, DAQ System Entwicklung und Charaterisierung und Performancestudien der produzierten Prototypen arbeiten. HEPHY ist eines dieser Institute und arbeitet federführend am digitalen ASIC Design, der Entwicklung von FPGA Firmware und Software des DAQ Systems mit und testet und studiert die Prototypen im Labor und bei Beamtests.

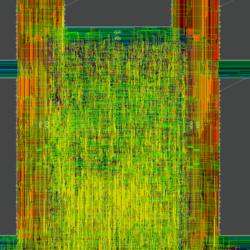

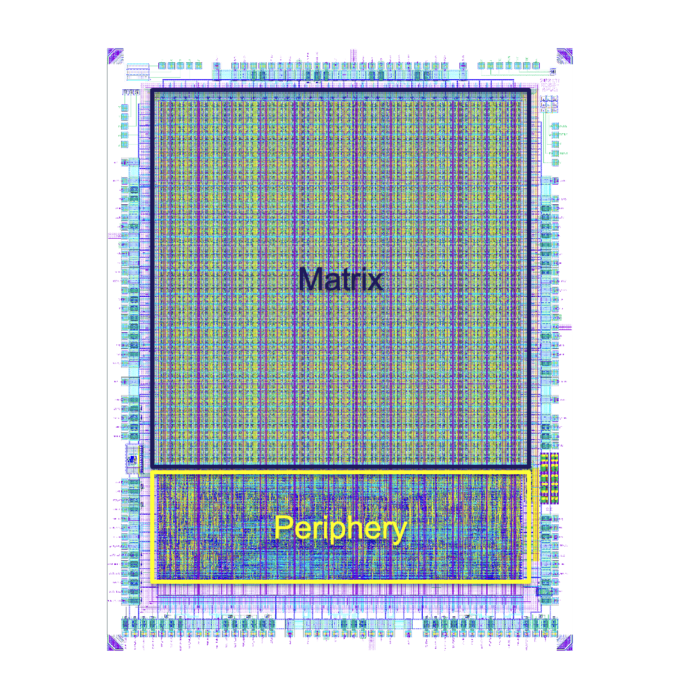

Der jüngste Prototyp, der RD50-MPW3, ist ein HV-CMOS-Chip im LFoundry 150nm Prozess mit Pixeln im Abstand von 62 μm, die sowohl digitale als auch analoge Ausleseelektronik in jeden Pixel integrieren. Die 64 x 64 Pixel auf diesem Chip sind in 32 Doppelspalten angeordnet und haben eine optimierte digitale Peripherie für eine effiziente Konfiguration und schnelle serielle Datenübertragung. Simulationen zeigen eine Leistungsaufnahme von 22 μW pro Pixel und 9 ns Zeitauflösung.

Belle II VTX Upgrade: Von Monopix zu Obelix

Ein weiteres aktuelles Projekt ist die Entwicklung eines auf monolitischen DMAPS Detektoren basierendes Upgrade des Belle II Vertex Detektors.

Für den Zeitraum 2026-2027 ist eine Aufrüstung des SuperKEKB Beschleunigers geplant, wobei eine Neugestaltung der Wechselwirkungsregion in Betracht gezogen wird. Darüber hinaus zeigt der derzeitige Belle-II-Vertexdetektor zwar seit Beginn der Datennahme im Jahr 2019 eine hervorragende Leistung, aber Simulationen zeigen, dass die erwartete Okkupanz (Anzahl gleichtzeitig feuender Kanäle) bei voller Luminosität des Beschleunigers die Grenzen der derzeitigen Technologie überschreiten. Aus diesen Gründen plant die Belle II-Kollaboration, den derzeitigen Pixel- und Streifen-Vertex-Detektor vollständig durch ein System zu ersetzen, das auf CMOS-Pixel Sensoren basiert.

Das geplante System soll DMAPS Pixelsensoren auf CMOS-Technologie mit der Bezeichnung OBELIX nutzen, die auf dem bereits existierenden Prototypen namens TJ-Monopix-2 basiert, welcher in der Vergangenheit für andere HEP-Anwendungen entwickelt wurde. Ein auf DMAPS Technologie basierender Vertex-Detektor wird das Materialbudget reduzieren und die räumliche Auflösung im Vergleich zum derzeitigen Detektor signifikant verbessern. Darüber hinaus wird er dank seiner schnellen Auslesearchitektur und der geringen Pixelabmessungen von nur 33x33 µm² eine extreme Verbesserung der Okkupanz im Vergleich zum jetzigen Detektor bieten. Außerdem wird durch einen großen On-Chip Hit Bufferspeicher eine hohe Triggerlatenz unterstützt, was die Implementierung komplexerer Algorithmen im Belle-II Triggersystem erlaubt.

Entwicklung von DAQ Systemen

Datenakquisition (DAQ) Systeme bezeichnet die Gesamtheit aus Elektronik-Hardware, Firmware und Software, die notwendig ist, um ein Detektor zu betreiben und seine Daten auszulesen. Diese meist als BE (backend) Elektronik bezeichneten Komponenten müssen mit dem eigentlichen (DMAPS) Sensoren und anderer FE (Front-End) Elektronik kommunizieren. Dies beinhaltet die Konfiguration der FE Elektronik und DMAPS Sensoren, die Slow Control (Messung von Spannungen, Strömen, Temperaturen,..), sowie die Übertragung und Verarbeitung der eigentlichen Nutzdaten aus einem Datenstrom mit hoher Bandbreite.

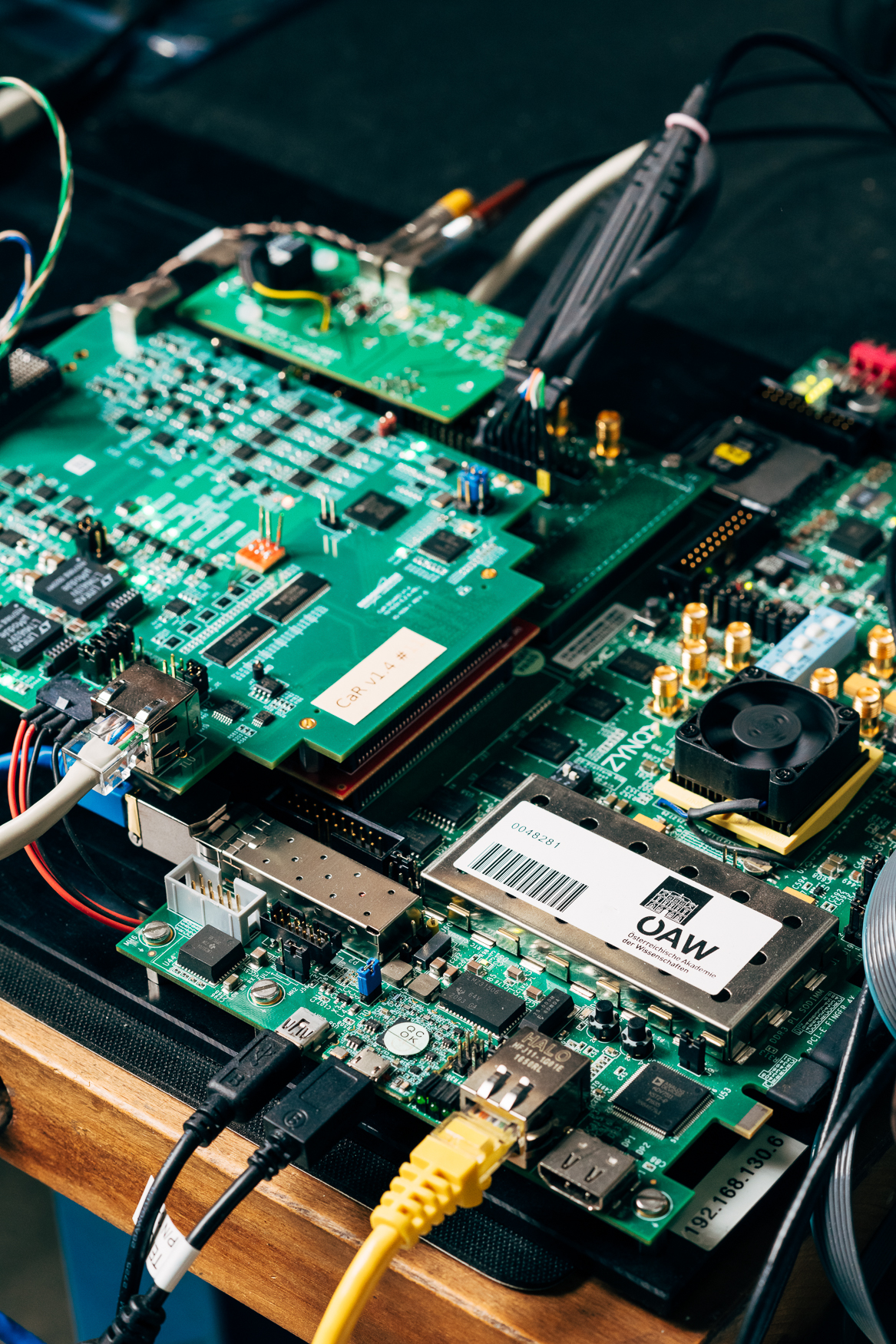

Zur Auslese der oben genannten RD50 und Belle-II Monopix/Opelix Sensoren entwickeln wir dafür maßgeschneiderte Elektronik, Firmware für FPGAs und die high-Level Software. Für die RD50 Sensoren wird dazu das sogenannte Caribou System verwendet, welches auf Xilinx Xynq 706 FPGA-Boards basieren und mit speziellen Adapterplatinen (CaR boards) mit den eigentlichen sensor-spezifischen Chipboards kommunizieren. Unsere Expertise liegt hier wiederum im Digitaldesign, der Entwicklung von low-level Firmware, welche robuste Datenübertragung selbst bei hoher Bitfehlerraten ermöglicht, sowie high-level Firmware, welche eine live-Kontrolle der Daten bzw. eine Integration in DAQ-Systeme wie EUDAQ ermöglicht.

Sowohl das Caribou-System der RD50-Chips als auch die sogenannten BDAQ53-Boards, die für die Auslese der Monopix2 Sensoren genutzt werden, können in unseren Labors betrieben werden. Mittels Alpha- bzw. Betastrahlung aus radioaktiven Quellen induzieren wir Signale in den DMAPS Sensoren, welche danach aufgezeichnet werden. Diese Messungen dienen üblicherweise als Vorbereitung für Beamtests am CERN, DESY, MedAustron oder anderen Beschleuniger-Zentren.